Quando dispositivos eletrônicos como celulares, smartwatches e outras tecnologias vestíveis são atualizados com modelos mais novos, uma quantidade considerável de lixo é produzida a cada ano.

Se as versões mais antigas pudessem ter sido atualizadas com novos sensores e processadores que se encaixam no chip interno do dispositivo, diminuindo o desperdício em termos de dinheiro e materiais, isso teria sido revolucionário. Considere um futuro mais sustentável em que smartphones, smartwatches e outras tecnologias vestíveis não sejam constantemente substituídos por modelos mais novos ou colocados na prateleira.

Em vez disso, eles podem ser atualizados com os mais novos sensores e processadores que simplesmente se encaixam no chip interno de um dispositivo, como peças LEGO adicionadas a uma estrutura existente. Esses chips reprogramáveis podem manter os dispositivos atualizados enquanto reduzem nosso desperdício digital.

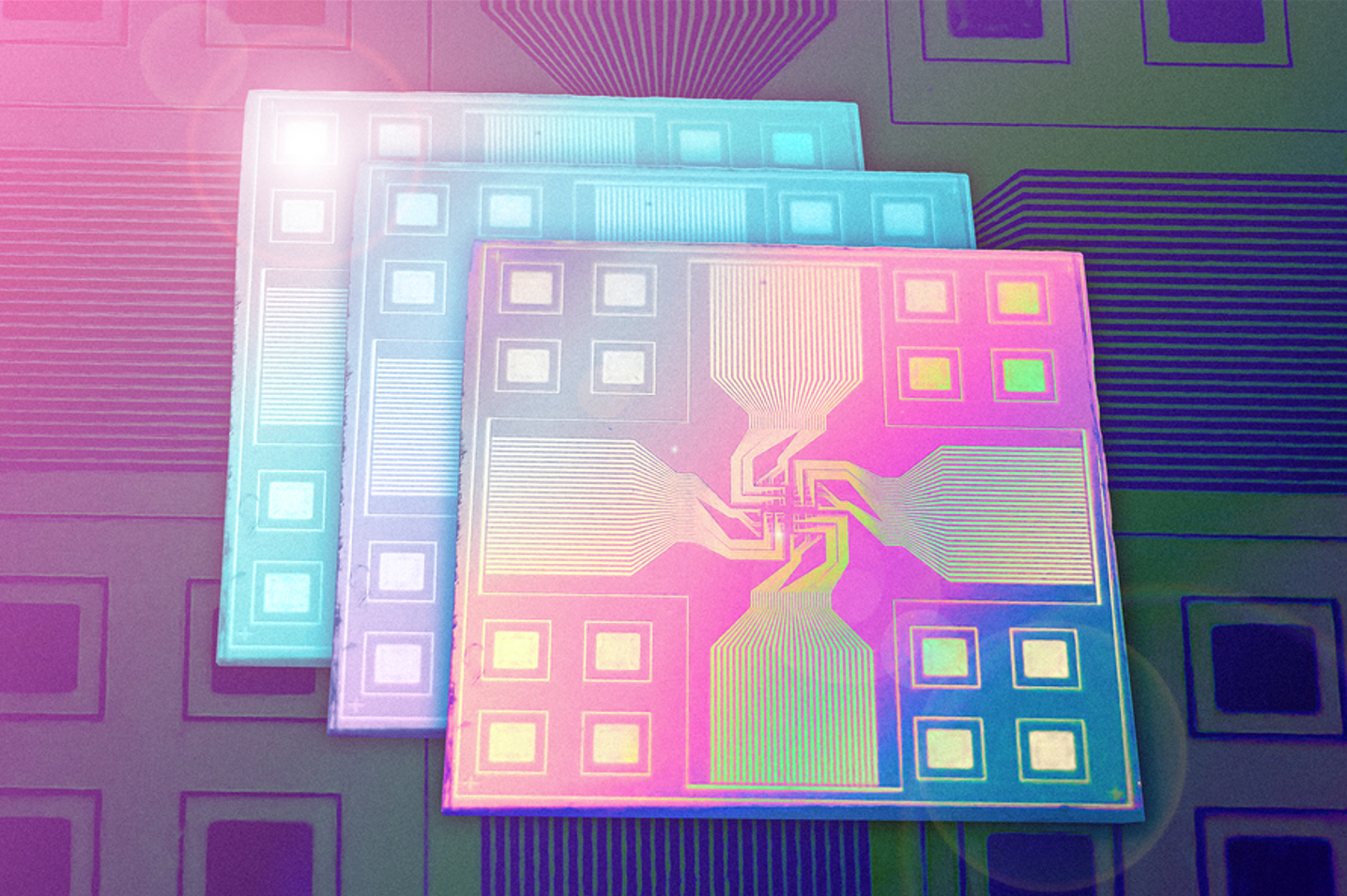

Com seu design semelhante a LEGO para um empilhável e personalizável inteligência artificial chip, os engenheiros do MIT agora deram um passo em direção a essa visão modular.

Este post analisará detalhadamente esse chip, suas configurações e suas implicações futuras.

Então, o que é um chip de Inteligência Artificial do tipo LEGO?

O próximo grande desenvolvimento que transformará o planeta é a inteligência artificial. Para produzir eletrônicos modulares e sustentáveis, os engenheiros do MIT criaram um chip de IA que se assemelha ao LEGO.

Para tornar o processo de adição de sensores adicionais ou atualização de processadores antigos mais simples, é um chip reconfigurável com várias camadas que podem ser sobrepostas ou comutadas.

Com base na combinação das camadas, os chips de IA “reconfiguráveis” podem ser expandidos indefinidamente. Portanto, esses chips podem reduzir o lixo eletrônico enquanto mantêm nossos dispositivos atualizados.

Agora, vamos explorar o design deste chip.

Design de chip

A arquitetura do chip AI é genuinamente excepcional porque combina camadas alternadas de componentes de processamento e sensores com LEDs (diodos emissores de luz), que permitem que as camadas do chip interajam visualmente.

A arquitetura inclui diodos emissores de luz (LED) que permitem a comunicação óptica entre as camadas do chip, bem como camadas alternadas de sensores e componentes de processamento. Os sinais são retransmitidos através dos níveis usando fio normal em outras arquiteturas de chip modular.

Essas conexões extensas tornam esses sistemas de empilhamento não configuráveis, pois são difíceis, se não impossíveis, de cortar e religar. Em vez de fios reais, o conceito do MIT transmite dados através do chip usando luz.

Como resultado, o chip pode ser reorganizado, com camadas que podem ser adicionadas ou subtraídas, por exemplo, para incluir novos sensores ou CPUs modernas. O novo conceito dos engenheiros combina sensores de imagem com matrizes de sinapses artificiais, e cada um deles é ensinado a reconhecer uma determinada letra, neste caso, M, I e T.

A equipe constrói um sistema óptico em vez de usar o método tradicional de transmissão de dados do sensor para o processo por meio de cabos físicos. Nesta abordagem, cada sensor e sinapses artificiais se combinam para formar um array que possibilita a comunicação entre as letras sem a necessidade de conexões físicas.

Os sinais entre as camadas são enviados via fio padrão no arranjo de chip modular usual. Esses chips convencionais não são reconfiguráveis porque tais arranjos de fiação intrincados são impossíveis de desconectar e reconectar.

Os pesquisadores aguardam ansiosamente a implementação de seu design inovador para avançar em dispositivos de computação, como sensores autossuficientes e vários outros eletrônicos, que não funcionam com um recurso central ou distribuído, como computação baseada em nuvem ou supercomputadores.

Configurações de chip

Um único chip foi criado pelos pesquisadores e seu núcleo computacional era aproximadamente do tamanho de um pedaço de confete de 4 milímetros quadrados.

O chip tem três “blocos” de reconhecimento de imagem colocados um em cima do outro, cada um com um sensor de imagem, uma camada de comunicação óptica e uma matriz de sinapses artificiais para identificar uma das três letras M, I ou T. Eles então projetou uma imagem de pixels gerada aleatoriamente no dispositivo e mediu a corrente elétrica que cada rede neural array gerado em resposta.

À medida que a corrente aumenta, a probabilidade de a imagem ser a letra que a matriz específica foi treinada para detectar aumenta

Os pesquisadores descobriram que, embora o chip pudesse discernir entre imagens nebulosas distintas, como entre as letras I e T, ele teve menos sucesso na classificação de imagens claras de cada letra. Quando a camada de processamento do chip foi prontamente substituída por um processador “denoising” superior, os pesquisadores descobriram que o dispositivo reconhecia corretamente as imagens.

No entanto, eles rapidamente substituíram a camada de processamento do chip por um processador habilidoso de remoção de ruído e, em seguida, produziram o clipe que detectou corretamente as imagens.

Como acreditam que existem inúmeras aplicações para esses dispositivos, os pesquisadores também planejam aumentar o poder de processamento dos chips e a capacidade dos sensores.

As aplicações são ilimitadas, acreditam os pesquisadores, e pretendem expandir as capacidades de detecção e processamento do chip.

Futuro disso

Em termos de trabalho futuro, os pesquisadores estão especialmente empolgados com a potencial adoção dessa arquitetura para computação de borda dispositivos como supercomputadores ou computação baseada em nuvem, o que abriria um mundo completamente novo de possibilidades.

À medida que a internet das coisas cresce, a demanda por dispositivos multifuncionais de computação de borda aumentará. A equipe acredita que porque dá muito computação de borda flexibilidade, seu design sugerido pode ajudar com isso.

Im para detectar imagens mais complexas ou para serem utilizadas em monitores eletrônicos de pele e saúde vestíveis, os pesquisadores também planejam aprimorar as capacidades de detecção e processamento do chip.

Os pesquisadores acham intrigante se os usuários pudessem montar o chip usando diferentes sensores e camadas de processamento que podem ser vendidos separadamente.

Dependendo de suas necessidades de identificação de imagem ou vídeo, o usuário pode escolher entre uma variedade de redes neurais.

Conclusão

A equipe destaca a computação de borda como um dos vários usos possíveis. Jeehwan Kim, professor associado de engenharia mecânica do MIT, prevê que a demanda por dispositivos multifuncionais de computação de borda aumentará significativamente à medida que entrarmos na era da internet das coisas baseada em redes de sensores.

No futuro, “nosso design de hardware sugerido permitirá uma tremenda adaptabilidade da computação de borda”.

Em conclusão, este chip muda o futuro e dá as boas-vindas a uma gama mais ampla de aplicações de IA.

Deixe um comentário