Inhaltsverzeechnes[Verstoppen][Show]

Wann elektronesch Geräter wéi Handyen, Smartwatches an aner wearable Technologie mat méi neie Modeller upgradéiert ginn, gëtt all Joer eng erheblech Quantitéit Dreck produzéiert.

Wann eeler Versioune kéinte mat neie Sensoren a Prozessoren aktualiséiert ginn, déi an den internen Chip vum Apparat knacken, d'Offall a Saache Suen a Material reduzéieren, da wier dat revolutionär gewiescht. Betruecht eng méi nohalteg Zukunft wou Smartphones, Smartwatches an aner wearable Technologien net stänneg duerch méi nei Modeller ersat ginn oder op de Regal gesat ginn.

Amplaz kënne se mat den neiste Sensoren a Prozessoren aktualiséiert ginn, déi einfach an den internen Chip vun engem Apparat snappen, sou wéi LEGO Zillen, déi an eng existent Struktur bäigefüügt ginn. Esou reprogramméierbar Chips kënne Geräter aktuell halen wärend eisen digitalen Offall reduzéieren.

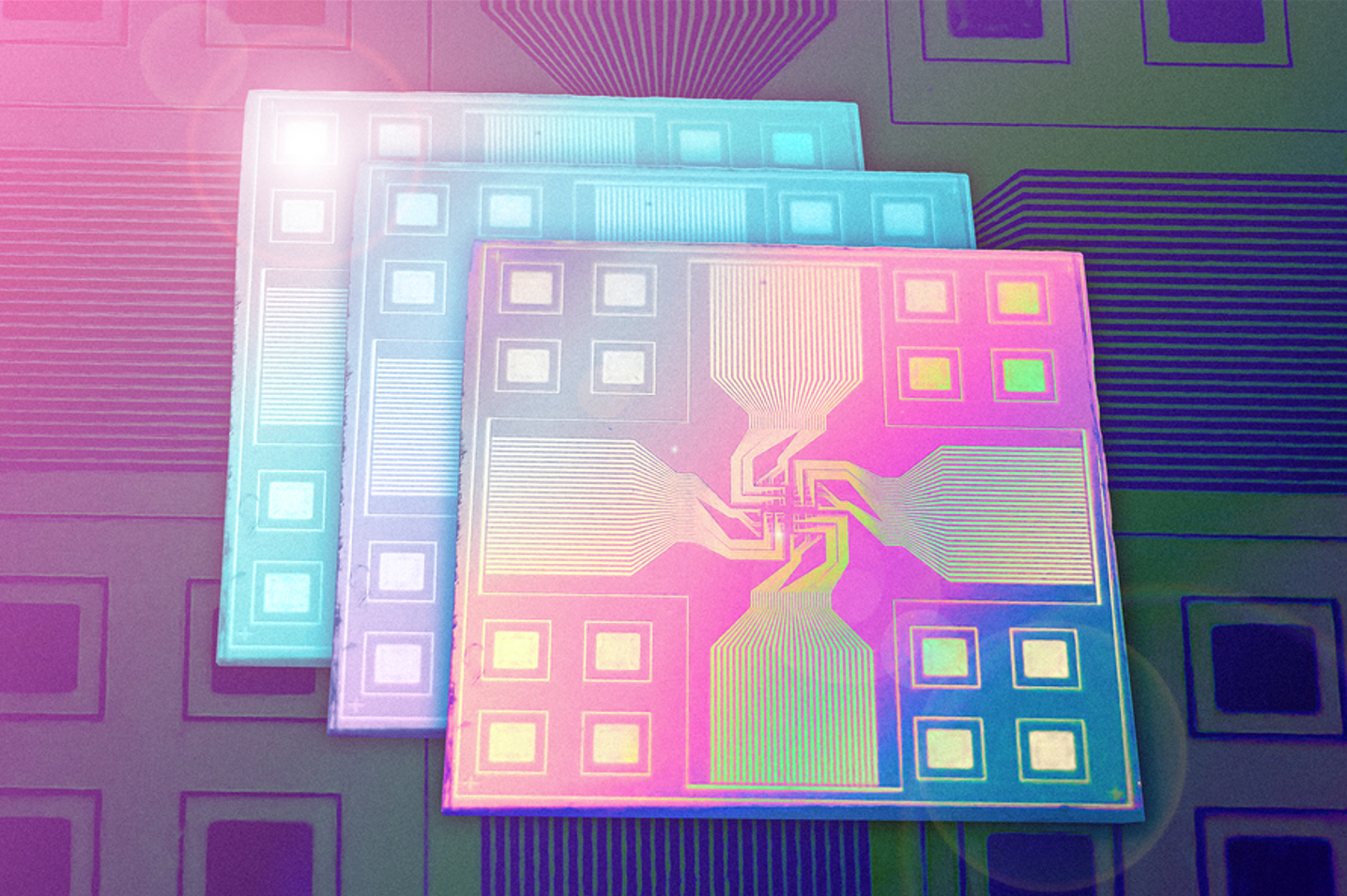

Mat hirem LEGO-ähnlechen Design fir eng stackbar, personaliséierbar Kënschtlech Intelligenz Chip, MIT Ingenieuren hunn elo e Schrëtt a Richtung dës modulare Visioun gemaach.

Dëse Post wäert e grëndleche Bléck op dësen Chip, seng Konfiguratiounen a seng zukünfteg Implikatioune kucken.

Also, wat ass e LEGO-ähnlechen Kënschtlech Intelligenz Chip?

Déi nächst grouss Entwécklung déi de Planéit transforméiere wäert ass kënschtlech Intelligenz. Fir modulär an nohalteg Elektronik ze produzéieren, hunn MIT Ingenieuren elo en AI-Chip erstallt, dee wéi LEGO gläicht.

Fir de Prozess fir zousätzlech Sensoren ze addéieren oder al Prozessoren z'erhéijen méi einfach ze maachen, ass et e rekonfiguréierbare Chip mat ville Schichten, déi openee geluecht kënne ginn oder gewiesselt kënne ginn.

Baséierend op der Kombinatioun vun de Schichten kënnen déi "rekonfiguréierbar" AI Chips onbestëmmt erweidert ginn. Dofir kënnen dës Chips den elektroneschen Offall reduzéieren wärend eis Apparater aktuell halen.

Elo, loosst eis den Design vun dësem Chip entdecken.

Chip Design

D'AI Chiparchitektur ass wierklech aussergewéinlech well se alternéierend Schichten vun der Veraarbechtung a Sensorkomponente mat LEDs (Liichtemittéierdioden) kombinéiert, déi d'Chipschichten visuell interagéieren.

D'Architektur enthält liicht emittéierend Dioden (LED) déi optesch Kommunikatioun iwwer d'Schichten vum Chip erméiglechen, souwéi ofwiesselnd Schichten vu Sensoren a Veraarbechtungskomponenten. D'Signaler ginn iwwer Niveaue weidergeleet mat normale Drot an anere modulare Chiparchitekturen.

Esou extensiv Verbindungen maachen esou Stackingsystemer net konfiguréierbar well se schwéier sinn, wann net onméiglech, ze schneiden an nei ze verbannen. Amplaz vun aktuellen Drot, iwwerdréit d'MIT Konzept Daten duerch den Chip mat Liicht.

Als Resultat kann den Chip nei arrangéiert ginn, mat Schichten déi bäigefüügt oder subtrahéiert kënne ginn, zum Beispill nei Sensoren oder modern CPUs. Den neie Konzept vun den Ingenieuren paréiert Bildsensoren mat kënschtlechen Synapse-Arrays, a jidderee vun hinnen gëtt geléiert e bestëmmte Buschtaf ze erkennen, an dësem Fall, M, I, an T.

D'Team konstruéiert en opteschen System anstatt déi traditionell Method ze benotzen fir Sensordaten op de Prozess duerch kierperlech Kabelen ze vermëttelen. An dëser Approche kombinéiere all Sensor a kënschtlech Synapse fir eng Array ze bilden déi d'Kommunikatioun tëscht de Bréiwer erlaabt ouni kierperlech Verbindungen.

D'Signaler tëscht de Schichten sinn iwwer Standard Drot am üblechen modulare Chip Arrangement geschéckt. Dës konventionell Chips sinn net reconfigurable well esou komplizéiert wiring Arrangementer sinn onméiglech ze trennen an rewire.

D'Fuerscher waarden ängschtlech op d'Ëmsetzung vu sengem banebriechenden Design fir Rechengeräter ze förderen, sou wéi selbststänneg Sensoren a verschidde aner Elektronik, déi net mat enger zentraler oder verdeelerer Ressource funktionnéieren wéi Cloud-baséiert Informatik oder Supercomputer.

Chip Konfiguratiounen

En Single-Chip gouf vun de Fuerscher erstallt, a säi computational Kär war ongeféier d'Gréisst vun engem Stéck Konfetti op 4 Quadratmillimeter.

Den Chip huet dräi Bilderkennungs-"Blocker" openee gesat, jidderee vun deenen e Bildsensor, eng optesch Kommunikatiounsschicht an eng kënschtlech Synapse-Array huet fir ee vun den dräi Buschtawen M, I oder T z'identifizéieren. projizéiert eng zoufälleg generéiert Bild vu Pixelen op den Apparat an huet den elektresche Stroum gemooss, deen all eenzel neural Netz Array generéiert als Äntwert.

Wéi de Stroum eropgeet, erhéicht d'Wahrscheinlechkeet datt d'Bild de Bréif ass, deen de spezifesche Array trainéiert gouf fir z'entdecken

D'Fuerscher hunn entdeckt datt wärend den Chip tëscht ënnerscheedlechen niwwelegen Biller z'ënnerscheeden, sou wéi tëscht de Buschtawen I an T, et manner Erfolleg hat fir kloer Biller vun all Bréif ze klassifizéieren. Wann d'Veraarbechtungsschicht vum Chip prompt mat engem superior "denoising" Prozessor ersat gouf, hunn d'Fuerscher entdeckt datt den Apparat d'Biller korrekt erkennt.

Wéi och ëmmer, si hunn d'Veraarbechtungsschicht vum Chip séier duerch e qualifizéierten Denoising-Prozessor ersat, an dunn hunn se de Clip produzéiert deen d'Biller korrekt erkennt.

Wéi se gleewen datt et eng Onmass Uwendunge fir dës Apparater sinn, plangen d'Fuerscher och d'Veraarbechtungskraaft an d'Sensorkapazitéit vun de Chips ze erhéijen.

D'Applikatioune sinn onbegrenzt, gleewen d'Fuerscher, a si wëlle de Sensing- a Veraarbechtungsfäegkeeten vum Chip ausbauen.

Zukunft vun et

Wat zukünfteg Aarbecht ugeet, sinn d'Fuerscher besonnesch opgereegt iwwer d'potenziell Adoptioun vun dëser Architektur Randberechnung Apparater wéi Supercomputer oder Cloud-baséiert Informatik, déi eng komplett nei Welt vu Méiglechkeeten opmaachen.

Wéi den Internet vun de Saachen wiisst, wäert d'Nofro fir multifunktionell Edge Computing Geräter eropgoen. D'Equipe gleeft, datt well et gëtt vill vun Randberechnung Flexibilitéit, seng proposéiert Design kann mat dësem hëllefen.

IFir méi komplex Biller z'entdecken oder an wearable elektronesch Haut- a Gesondheetsiwwerwaachung ze benotzen, plangen d'Fuerscher och d'Sensing- a Veraarbechtungsfäegkeeten vum Chip ze verbesseren.

D'Fuerscher fannen et interessant wann d'Benotzer den Chip selwer mat verschiddene Sensoren a Veraarbechtungsschichten zesummesetzen, déi separat verkaaft kënne ginn.

Ofhängeg vun hire Bedierfnesser fir e Bild- oder Video-Identifikatioun, kann de Benotzer aus enger Vielfalt wielen neural Netzwierker.

Konklusioun

D'Team zielt Rand Computing als ee vun de verschiddene méigleche Gebrauch aus. De Jeehwan Kim, en Associé Professer fir mechanesch Ingenieurswiesen um MIT, virausgesot datt d'Nofro fir multifunktionell Edge Computing Geräter wesentlech eropgeet wéi mir an d'Ära vum Internet vu Saachen baséiert op Sensornetzwierker goen.

An der Zukunft, "eise proposéierte Hardware-Design erlaabt eng enorm Adaptabilitéit vum Edge Computing."

Als Conclusioun ännert dësen Chip d'Zukunft a begréisst eng méi breet Palette vun AI Uwendungen.

Hannerlooss eng Äntwert